发布日期:2021-2-20 来源:本站 返回列表

成果简介:

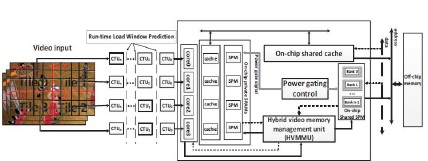

与H.264相比,下一代视频编码标准(HEVC)为高分辨率视频提供了更好的压缩率,但却大大增加了对计算能力和内存带宽的需求。为了解决上述问题,本专利提出了一种面向多核处理器架构的片上混合存储架构及其动态资源管理方法。该片上存储结构同时具有硬件控制的高速缓存cache和软件可控的便笺式存储器(scratchpad memory,SPM)。专利提出了一种运行时的任务负载预测算法,用于有效地识别HEVC编码搜索窗口中访问最频繁的内存区域,并将其动态加载入有限的SPM存储空间中,利用较少的片上存储资源实现高能效的HEVC编码。在此基础上,本专利提出根据数据的访问情况给每一个SPM区域分配合理的功耗状态,从而进一步降低片上静态功耗。专利提出的方案针对HEVC的访存特点设计,能够在保证编码实时性的前提下,明显降低HEVC编码的能耗,促进HEVC在低功耗嵌入式多媒体设备上的发展。

应用情况:

HEVC作为下一代高清视频编码标准,在数字医疗、计算机视觉、多媒体等领域具有广阔的应用空间。然而其较高的计算负载与能耗限制了基于软件的HEVC编码器在资源受限的嵌入式系统中的广泛应用。

我们在实验室原型系统下,采用HEVC测试模型HM 14.0,使用verilog HDL和ModelSim来实现HVMMU,进行实验评估,并用Xilinx XPower分析仪来测量硬件模块的功耗,实验结果表明,我们所提出的内存管理框架支持高速并行HEVC处理,其芯片存储容量小得多,达到76.23%的芯片泄漏能量的节省,为整个内存子系统节省了33.31%的能量。